中新网上海新闻6月25日电(记者 李佳佳)日前,合见工软作为中国数字EDA/IP龙头企业在上海召开了“2025合见工软新产品发布会暨技术研讨会”,会上展示了下一代国产EDA技术的重大革新进展,并正式发布了多款国产自主自研EDA及IP产品。

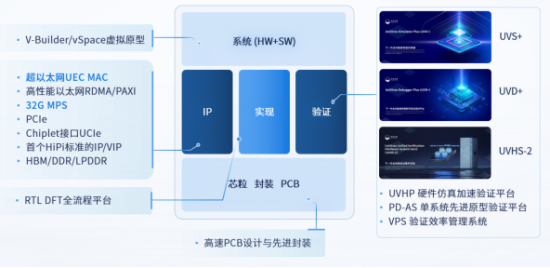

从断供后的开放免费试用,到快速发布多款可比肩国际标杆水平的EDA工具,合见工软以一套组合拳快速应对禁售的挑战,重塑了中国EDA自主可控的新态势。本次合见工软正式发布的五款创新产品包括:数字验证下一代硬件产品,下一代全场景验证硬件系统UniVista Unified Verification Hardware System Gen2(UVHS-2);国产数字仿真调试EDA重大进展,下一代全功能高性能数字仿真器UniVista Simulator Plus (UVS+)和下一代全功能高效能数字验证调试平台UniVista Debugger Plus (UVD+);全国产自主知识产权高速接口IP解决方案,推动智算互联的超以太网IP解决方案UniVista UEC MAC IP以及先进工艺多协议兼容、集成化传输接口SerDes IP解决方案。

合见工软现有产品已覆盖数字芯片EDA工具、系统级工具及高端IP,是国内唯一一家可以完整覆盖数字芯片验证全流程,DFT可测性设计全流程,并同时提供先进工艺高速互联IP的国产EDA公司。自成立以来,合见工软一直以国际先进水平为目标,多产品线并行研发,为中国半导体企业提供了芯片硅前和硅后的高性能EDA工具和IP解决方案。

此次发布的下一代EDA战略,合见工软将数字验证最核心的基础工具――数字仿真/调试器,及支持大规模芯片设计的高端硬件验证平台,均实现了架构级迭代创新,是国产EDA技术创新的重大进展,多项性能比肩国际标杆水平,目标打破数字高端大芯片验证EDA的国际厂商垄断。

同时,合见工软已在国内自研IP领域取得了快速的技术进展和客户增长,在国内自主自研高速接口IP的市场份额中已居前列。目前,合见工软的高速接口IP解决方案已实现了国产化技术突破,支持国内外先进工艺,并得到多家商业客户的成功流片和数百家客户的商业部署。合见工软的智算芯片互联IP解决方案,覆盖国内外先进标准,助力智算、HPC、通信、自动驾驶、工业物联网等领域大算力芯片的性能突破及爆发式发展。

合见工软联席总裁郭立阜表示:“国产EDA工具链的自主可控对于打造安全、高效、可持续的芯片产业环境至关重要,而芯片设计验证占据总设计周期的70%以上,直接影响产品上市时间和质量,只有高性能与可靠性并重的验证工具,才是保障客户项目成功的关键。合见工软数字仿真及调试工具经过与国内头部芯片设计企业紧密合作,历经三年淬炼迭代,第二代UVS+与UVD+工具平台带来性能上的飞跃,全自研架构自主可控带来可靠性的全面提升,提升供应链韧性,为中国芯片设计项目保驾护航,抵御外部风险,为‘中国芯’的创新提供沃土。”(完)

注:请在转载文章内容时务必注明出处!

编辑:李秋莹